Parasitic Extraction and Post-Layout Simulation

Authors: Michael Cunningham, Joseph Chong, and Dr. Dong S. Ha

In order to get a good idea of realistic parameters in our design, we run RCX which can estimate and add to your design the parasitic resistances (R), capacitances (C), self inductances (L), and mutual inductances (K). We are only interested in RC parasitics. You will need a successful LVS before RCX.

Parasitic Extraction

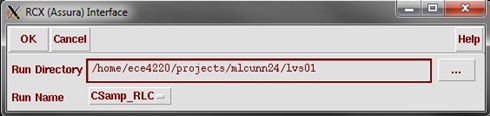

1. In the layout window, go to Assura → Run RCX....

2. Keep the "Run Directory" the same as the LVS run directory, make sure the run name is correct, and select OK. If you're unsure of the path, run LVS before RCX and it will be set automatically next time you run RCX.

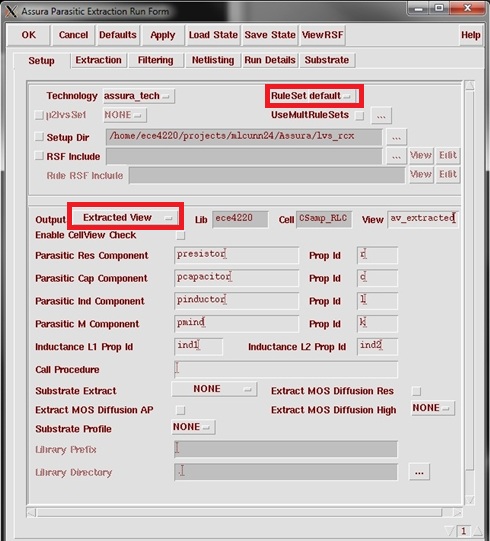

3. The Assura Parasitic Extraction Run Form will appear.

4. In the Setup tab:

Change "Rule Set" to default.

Change "Output" to Extracted View.

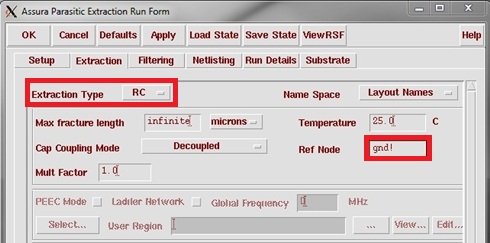

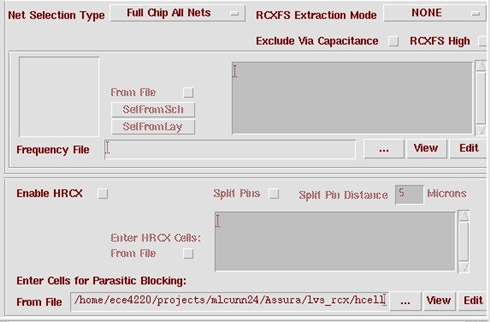

5. In the Extraction tab:

a. Change the "Extraction Type" to RC .

b. Change "Ref Node" to gnd! (if we had used a substrate connection it would be sub!).

c. Make sure the max fracture length is infinite , the coupling mode is decoupled , and multiplication factor is 1.0 (these should be the default).

d. Next to "From File", select "..." and add hcell (Assura lvs_rcx; hcell is in the right column).

6. Select OK. A progress form will appear in the lower right-hand corner or your screen.

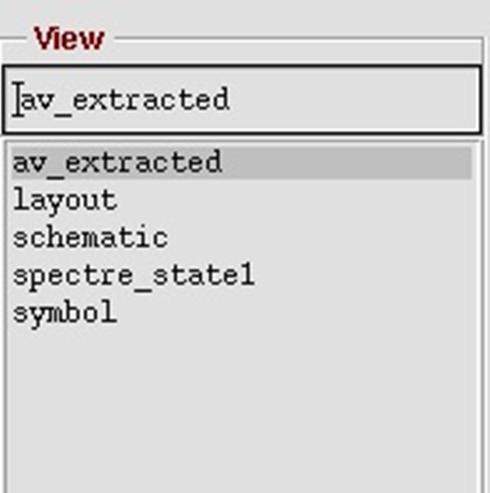

7. Once the extraction finished, you should see an "av_extracted" view in your library manager for the cell.

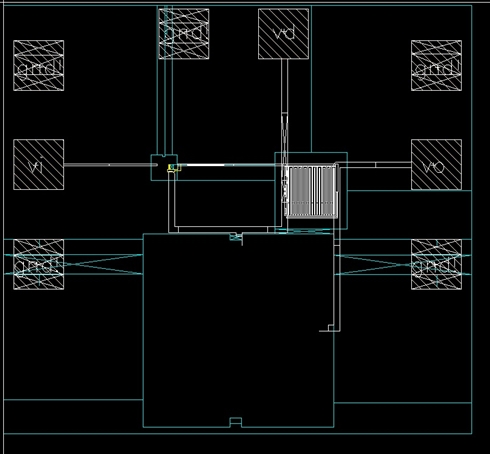

8. Note: If you open the av_extracted view, you can see the parasitic extraction in detail. If you zoom in close enough, you can see the values.

Post-Layout Simulation

Post-layout simulation is fairly simple, all you really need to do is switch to the av_extracted view:

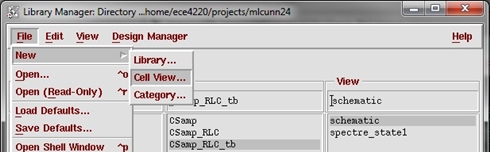

1. Go to the Library Manager, select the testbench for your design and add a new cell view (File → New → Cell View...). You can also do this through the icfb window.

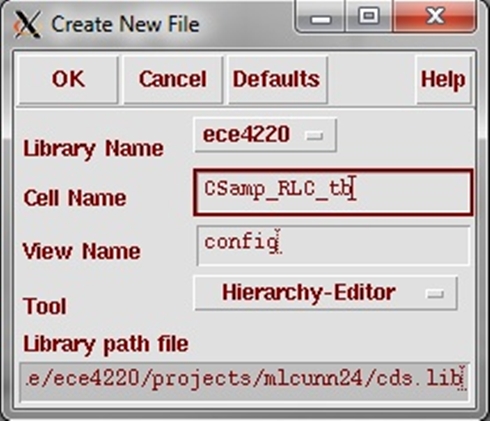

2. In the next window, change the "Tool" to "Hierarchy-Editor". Make sure the "View Name" is now "config".

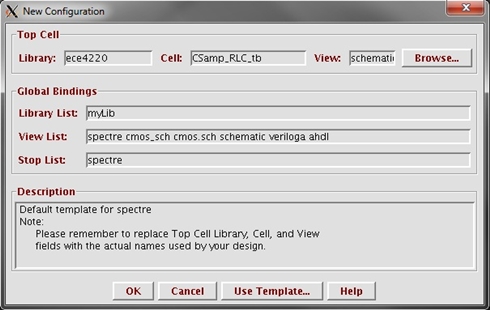

3. In the New Configuration window, browse and select the schematic view. Then click the "Use Template..." button and select "spectre" in the new window. Select OK.

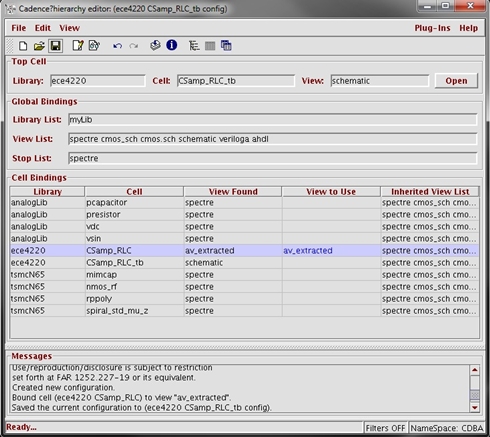

4. The hierarchy editor will populate with cell bindings from the top cell. Select the appropriate cell (your circuit level, not the testbench) and enter "av_extracted" into the "View to Use" box. Save your design using the floppy disk symbol in the top toolbar and close the window.

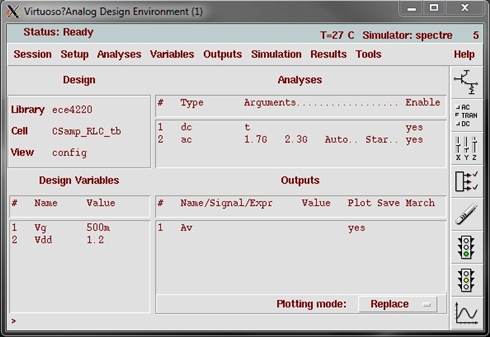

5. Now go to your testbench schematic and start the Analog Design Environment. Change the "View Name" to config either through Setup → Design... or by pressing the emitter follower symbol on the right toolbar (at the top). You may need to reload your state.

6. Now run your simulation and compare the layout to the circuit (use the "Append" feature for the plotting mode and run the simulation each view).

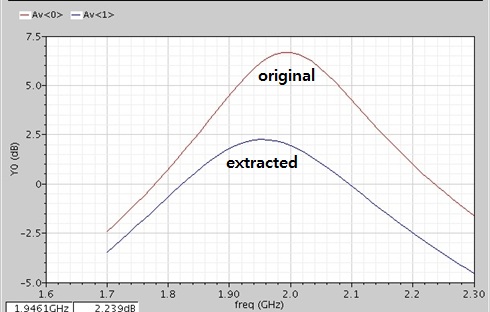

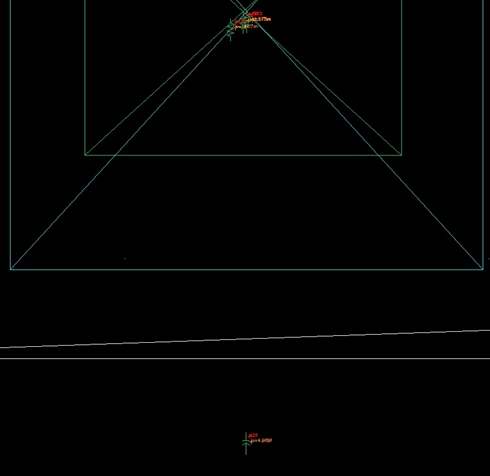

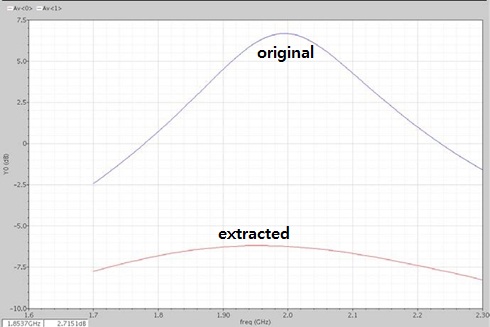

7. You might get a very poor result (shown below). You will need to fix your layout to reduce parasitic values.

8. You have just ran simulation with RC extraction. If the performance is not satisfactory, then either it’s too much R or too much C. Increase line width / number of vias to reduce R. Reduce metal area / overlapping metals to reduce C.

9. Remember to run RCX again so that the av_extracted view contains the new design. Overwrite the av_extracted view so that it is automatically updated. If you want to keep a previous design, the easiest thing to do is to save the cell as a backup:

10. Assume that we have somewhat improved the layout. Re-simulate with the "config" view. The performance is still degraded, but it is nearly there.