Front End Design Using Synopsys Tools - Part 2

Author: Hetaswi Vankani, Dr. Dong S. Ha

Tool: Library Compiler, VCS and DVE

NOTE: The files downloaded must not be saved or used in .txt format. Please save it in the format as mentioned in the tutorial.

Analyze and Compile

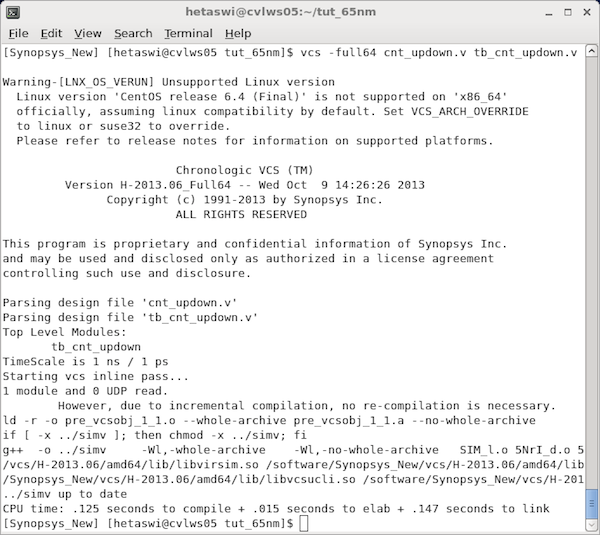

1. Make sure that ‘[Synopsys_New]’ appears in the prompt, if not type ‘Synopsys_New’

2. Next, compile the Verilog files. This is done using VCS which is Verilog Compiler Simulator from Synopsys.

3. Type:

vcs –full64 cnt_updown.v tb_cnt_updown.v

(The option –full64 allows the tool to invoke its bin file for 64-bit machine. This option has not been set by default for computing system at VT)