Front End Design Using Cadence Tool - Analyze and Compile

Authors: Hetaswi Vankani, Adithya Venkatramanan,and Dr. Dong S. Ha

Tool: NCVerilog and SimVision (also called ncsim)

1. Analyze and Compile

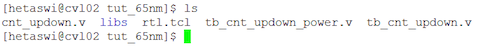

a. Creating project directory - First create a directory by any relevant name. In the example shown below, it is called 'tut_65nm' as it is a tutorial designed for automation at 65nm.

As one can see, this folder will be the work/project directory for this tutorial. It has the following files:

NOTE: The file downloaded must not be saved or used in .txt format. Please save it in the format as mentioned in the tutorial.

i. cnt_updown.v - Verilog code for an updown counter.

ii. tb_cnt_updown.v - Test bench for the updown counter. Make sure that the testbench has the line $dumpfile(“./updown_counter.dump”);. File named ‘updown_counter.dump’ will be generated at the end of the compilation process and it is used during waveform analysis for functional verification. The line $dumpvars (0, tb_cnt_updown); makes sure that the values of all variables are available in the .dump file.

iii. rtl.tcl – This file contains the set of commands to be executed by Cadence’s RTL Compiler. This is not relevant to the current tutorial, but will be used in the tutorial on synthesis. Important note: After downloading rtl.tcl to your project directory, set the ‘lib_search_path’ in the script (i.e., rtl.tcl) appropriately. It should be /home/<your PID>/<project_directory>/libs. For example in the current version of the script, it has been set to /home/hetaswi/tut_65nm/libs.

iv. libs/ - This directory contains the libraries used for this tutorial. Liberty format files (.lib) will be required for this tutorial. For the purpose of tutorial, nominal PVT has been chosen. VT students can create a soft link to the library in the libs folder in their directory using the command

a. If current directory is project_dir: cd libs

b. cp /software/PDK/65nm_TSMC/Mosis_Doc/65nmLibs/tcbn65gplus/tcbn65gplus_frontendzipped/tcbn65gplus_140b_nldm/TSMCHOME/

digital/Front_End/timing_power_noise/NLDM/tcbn65gplus_140b/tcbn65gplusbc0d88.lib tpdn65gpgv2od3_sdbc.lib ./tcbn65gplusbc0d88.

c. cp /software/PDK/65nm_TSMC/Mosis_Doc/65nmLibs/tpdn65gpgv2od3_sd/tpdn65gpgv2od3_sd/tpdn65gpgv2od3_sd_200a_nldm/

TSMCHOME/digital/Front_End/timing_power_noise/NLDM/tpdn65gpgv2od3_sd_200a/ tpdn65gpgv2od3_sdbc.lib ./tpdn65gpgv2od3_sdbc.lib

d. cd ..

Step (d) is important because the tool must be invoked from the project directory for the purpose of consistency and getting relative paths in tutorials to follow, correct.

NOTE: If you are remotely connecting using windows system and want to save the files on your CVL machine, refer to the note in tutorial01.

B. Once all the inputs are available. If you are a VT student, type ‘Cadence’ (Note: capital c in Cadence) to set path to the various libraries and bins required to start any Cadence tool. If there is a problem in invoking the tool, contact sysadmin, it possible that the paths may have changed. ‘[Cadence]’ in the prompt indicates that the paths to Cadence tools have been set.

C. Having typed Cadence, the following command with compile the Verilog source files: (make sure that you are in your project directory)

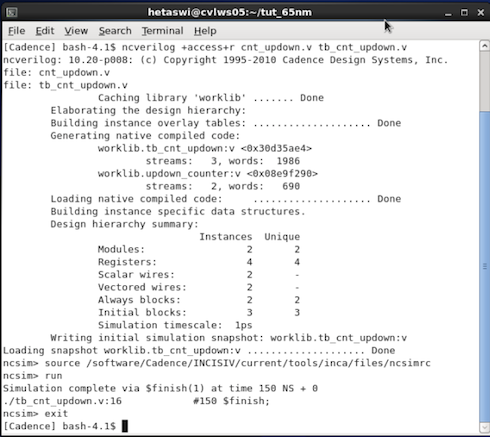

ncverilog + access + r cnt_updown.v tb_cnt_updown.v

A message as shown in figure 2 will appear.

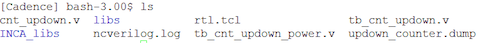

The output files generated as a results of this command are:

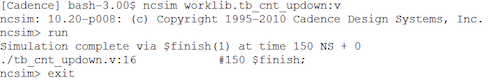

i. INCA_libs/ - This directory contains the sanpshot of simulations. So if you type: ncsim worklib.tb_cnt_updown:v The following results appears:

ii. Updown_counter.dump - This file will be used by the simulator to display waveform.

iii. ncverilog.log - This is the log file generated by ncverilog showing the execution of analyze and compile.

Comments to: ha@vt.edu