Back End Design Using Cadence Tool – Physical Implementation

Authors: Hetaswi Vankani, Adithya Venkatramanan, and Dr. Dong S. Ha

Tool: Encounter Digital Implementation (encounter)

Import Design

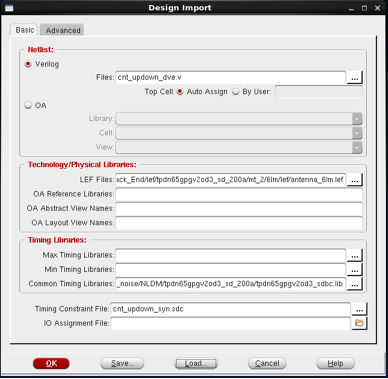

1. To start with, the paths to LEF, timing libs and LEF must be set correctly. As shown in the picture below:

File → Import Design

a. Type 'Cadence' in unix prompt. This is to set path to the bin files of various Cadence tools. [Cadence] should appear in the prompt. Next type ‘encounter’.

b. In basic tab:

i. Verilog file: cnt_updown_dve.v (this is the modified synthesis file with PADS inserted)

ii. LEF file: The paths mentioned in point 1 must be set here.

iii. Timing libs: paths mentioned in point 1 must be set here.

iv. Timing constraints file: cnt_updown_syn.sdc (this is the modified constraints file with signal names changed as per the changes in the synthesized netlist)

v. Next, changes in advanced tab.

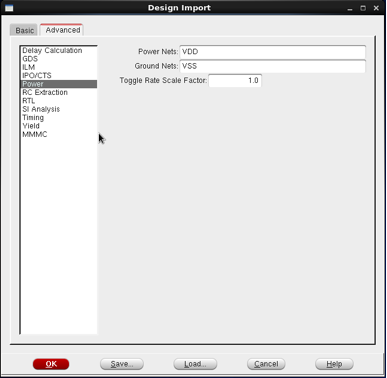

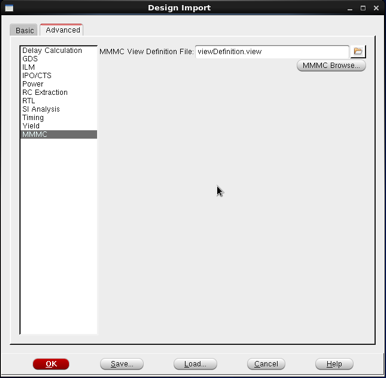

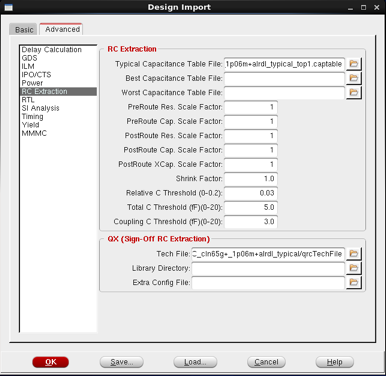

2. Changes in advanced tab:

a. Power: Power Nets: VDD and Ground Nets: VSS

b. MMMC: Load the viewDefinition.view file

c. RC Extraction: Set the path to the capacitance table and qrcTech file correctly.

3. Hit 'Save' and save the design as default.conf. Next time EDI is invoked, one can ‘Load’ the default.conf file to set the parameters.

4. Click OK

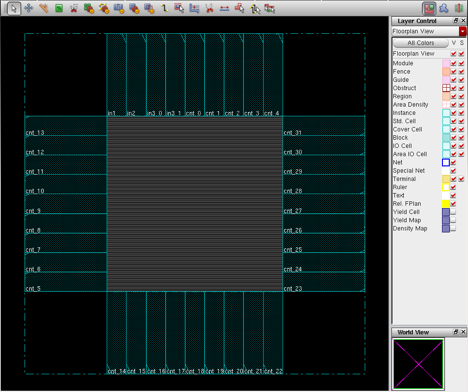

On setting the various paths, the design loaded appears as shown in the pic below